Двухуровневая организация кэша

Предельно достижимая емкость кэш-памяти ограничена не только ее ценой, но и электромагнитной интерференцией (см. "Часть I Оперативная память. Устройство и принципы функционирования оперативной памяти. RDRAM Rambus DRAM – Rambus-память"), налагающей жесткие ограничения на максимально возможное количество адресных линий, а значит – на непосредственно адресуемый объем памяти. В принципе, мы можем прибегнуть к мультиплексированию выводов или последовательной передаче адресов (как, например, поступили разработчики Rambus RDRAM), но это неизбежно снизит производительность и доступ к ячейке кэш-памяти потребует более одного такта, что не есть хорошо.

С другой стороны, двух портовая статическая память действительно очень дорога, а одно-портовая не в состоянии обеспечить параллельную обработку нескольких ячеек, что приводит к досадным задержкам.

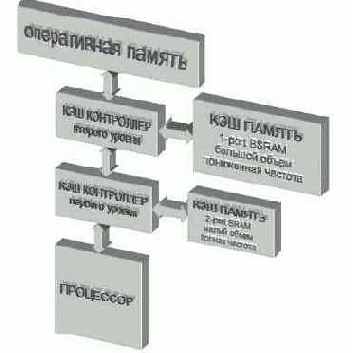

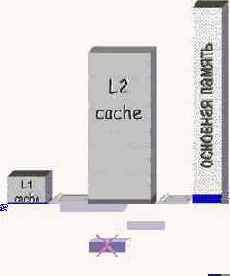

Естественный выход состоит в создании многоуровневой кэш-иерархии (см. рис. 0х013). Большинство современных систем имеют как минимум два уровня кэш памяти. Первый, наиболее "близкий" к процессору (условно обозначаемый Level 1

или сокращенно L1), обычно реализуется на быстрой двух портовой синхронной статической памяти, работающей на полной частоте ядра процессора. Объем L1-кэша весьма не велик и редко превышает 32 Кб, поэтому он должен хранить только самые-самые необходимые данные. Зато на обработку двух полно разрядных ячеек уходит всего один такт. (Внимание: процессоры x86 оснащаются не истинно двух портовой памятью! Двух портовый у нее лишь интерфейс, а ядро памяти состоит из нескольких независимых банков, – обычно восьми, реализованных на одно-портовый матрицах, и параллельный доступ возможен лишь к ячейкам разных банков. см. "Оптимизация обращения к памяти и кэшу. Стратегия распределения данных по кэш-банкам.")

Между кэшем первого уровня и оперативной памятью расположен кэш второго уровня (условно обозначаемый Level 2

или сокращенно L2). Он реализуется на одно-портовой конвейерной статической памяти (BSRAM) и зачастую работает на пониженной тактовой частоте.

Поскольку одно- портовая память значительно дешевле, объем L2 кэша составляет сотни килобайт, а зачастую достигает и нескольких мегабайт! Между тем скорость доступа к нему относительно невелика (хотя, естественно, многократно превосходит скорость доступа к основной памяти).

Во-первых, минимальной порцией обмена между L1 и L2 кэшем является отнюдь не байт, а целая кэш-линейка, на чтение которой уходит в среднем 5 тактов частоты кэша второго уровня (напоминаем, что формула BSRAM памяти выглядит так: 2-1-1-1). Если L2-кэш работает на половинной частоте процессора, то обращение к одной ячейке займет целых 10 тактов. Разумеется, эту величину можно сократить. В серверах и высокопроизводительных рабочих станциях кэш второго уровня чаще всего работает на полной частоте ядра процессора и зачастую имеет учетверенную разрядность шины данных, благодаря чему пакетный цикл обмена завершается всего за один такт. Однако и стоимость таких систем соответствующая.

Рисунок 12 0х013 Двух уровневая кэш-иерархия

Включающая (inclusive) архитектура.

Кэш второго уровня, построенный по inclusive-архитектуре, всегда дублирует содержимое кэша первого уровня, а потому эффективная емкость сверхоперативной памяти обоих иерархий равна: L2.CACHE_SIZE – L1.CACHE.SIZE + L1.CACHE.SIZE == L2.CACHE.SIZE.

Давайте рассмотрим, что происходит в системе, когда при полностью заполненном кэше второго уровня, процессор пытается загрузить еще одну ячейку. Обнаружив, что все кэш-линейки заняты, кэш второго уровня избавляется от наименее ценной из них, стремясь при этом найти линейку, которая еще не была модифицирована, поскольку в противном случае еще придется выгружать в основную оперативную память, а это – время.

Затем кэш второго уровня передает полученные из памяти данные кэшу первого уровня. Если кэш первого уровня так же заполнен под завязку ему приходится избавляться от одной из строк по сценарию, описанному выше.

Таким образом, загруженная порция данных присутствует и кэш-памяти первого уровня, и в кэш-памяти второго, что не есть хорошо.

Между тем, практически все современные процессоры (AMD K6, P-II, P-III) построенные именно по включающей архитектуре.

Рисунок 13 0х014 0х015 inclusive- (слева) и exclusive- (справа) архитектуры

Исключающая (exclusive) архитектура.

Кэш-подсистема, построенная по exclusive-архитектуре, никогда не хранит избыточных копий данных и потому эффективная емкость сверхоперативной памяти определяется суммой

размеров сверхоперативной памяти всех иерархий.

Кэш-первого уровня никогда не уничтожает кэш-линейки при нехватке места. Даже если они не были модифицированы, – данные в обязательном порядке вытесняются в кэш-второго уровня, помещаясь на то место, где находилась только что переданная кэшу первого уровня линейка. Т.е. кэш первого и кэш второго уровней как бы обмениваются друг с другом своими линейками, а потому сверхоперативная память используется весьма эффективно.

Причем, во избежание падения производительности, процесс обмена должен происходить параллельно, а не через промежуточный буфер, иначе время загрузки данных из кэш-памяти второго уровня увеличиться на несколько тактов, необходимых для выгрузки линейки в промежуточный буфер.

На сегодняшний день эксклюзивная кэш-подсистема реализована в одном лишь процессоре AMD Athlon, да и то не с первых моделей (см. так же. "Оптимизация обращения к памяти и кэшу. Влияние размера обрабатываемых данных на производительность. Особенности кэш-подсистемы процессора AMD Athlon")

Промах кэша первого уровня может стоить многих тактов процессора и даже очень многих, если искомых данных не окажется и в кэше второго уровня. Конвейерные процессоры, к семейству которых принадлежит и Pentium, в той или иной степени компенсируют падение производительности. Благодаря конвейеру промах чтения не вызывает остановки работы процессора – во время загрузки данных могут выполняться и другие команды. При условии, что поток кода не содержит неустранимых зависимостей, производительность программы ничуть не снизится.Правда, на практике такая ситуация наблюдается очень редко. Не мудрено – если мы обращаемся к данным, то явно затем, чтобы использовать их в самом ближайшем будущем.